AMD、Zen 6 EPYC VeniceでN2 (2nm)プロセスを採用。Zen 6 Ryzenはどうなるか

AMDは、Zen 6世代EPYCにて、TSMCのN2 (2nm)プロセスを採用することを発表しました。

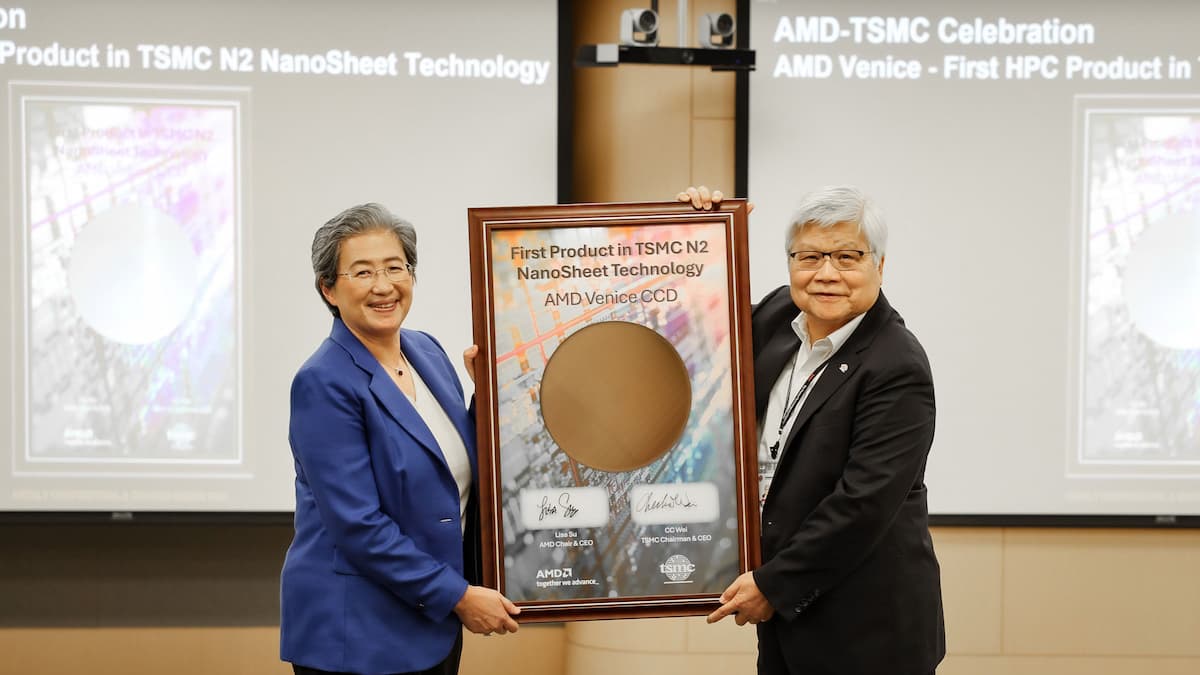

次世代(第6世代)のAMD EPYCプロセッサー(コードネーム: Venice)は、TSMCの先端技術、2nm (N2)プロセスでテープアウトされ、立ち上げに成功した初のHPC製品であることを発表いたします。これは当社(AMD)とTSMCが最先端のプロセス技術で新しいアーキテクチャを共同で最適化し、半導体製造における強力なパートナーシップであることを示すものです。また、データセンター向けCPUロードマップにおける大きな前進を意味し、『Venice』は2026年の発売に向けて順調に進んでいます。 さらに、アリゾナ州にあるTSMCの新しい製造施設において、第5世代AMD EPYC CPU製品の立ち上げと検証にも成功したことを発表いたします。これは、米国内での製造への取り組みを明確に示すものです。 ― AMD |

第5世代EPYCは、Zen 5コアにTSMCのN4X (4nm、正確には改良版5nm)、Zen 5cコアにN3E (3nm)を採用していました。コンシューマー向けのRyzen 9000シリーズデスクトップCPUもN4Xです。

今回、AMDは、Zen 6アーキテクチャの第6世代EPYC『Venice』にて、CCDにN2プロセスを採用することを明らかにしました。

一般PCユーザーとして気になってくるのがコンシューマー向け次世代CPUのZen 6 Ryzenがどうなるかでしょう。この発表からしてZen 6 RyzenでもN2プロセスの採用を期待したいところですが、どうなるでしょうか。